In which type of storage will the compiler preferentially place frequently accessed variables?

Which one of the following statements best describes the function of vector catch logic?

Which of the following would enable the use of a symmetric multiprocessing (SMP) operating system?

Which of the following memory attributes, specified in a translation table entry, could be used to protect a page containing a read-sensitive peripheral from speculative instruction fetches?

Under which of the following data-sharing scenarios would cache maintenance operations be necessary?

An ARMv7 implementation might include the VFPv4-D32 floating point extension. What does the '32' indicate?

In Architecture ARMv7-A which one of the following has a known physical address at power-on reset?

In a loop termination test, how might a programmer indicate to the compiler that the loop iteration count limit is divisible by four?

Cortex-A series processors contain event counting hardware which can be used to profile and benchmark code. The counters for these are programmed using:

Which events would be counted using the Performance Monitoring Unit (PMU) in order to measure the data cache efficiency of an application?

In the ARM instruction set what is the maximum branch distance for a Branch or Branch and Link instruction?

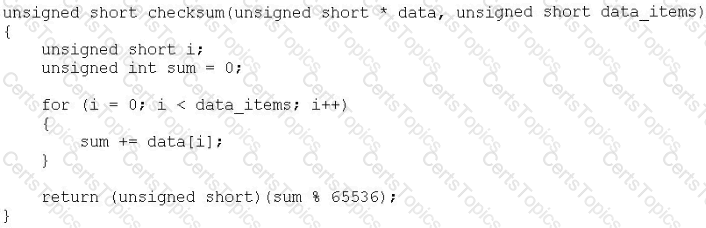

In an ARMv7-A system, the following C function calculates a simple checksum for an input data packet of variable length. The checksum is defined to be the sum of all of the 16-bit data items in the packet modulo 65536. The parameter data_items contains the number of 2-byte data items in the packet, and it cannot be zero by design.

When using an ARM compiler, which TWO of the following optimizations could improve the performance of this code? (Choose two)

An external debugger would need to clean the contents of the processor data cache in which of the following cases?

Which one of these statements is TRUE about code running on final hardware without a debugger attached?

An undefined instruction will cause an Undefined Instruction exception to be taken when:

An Advanced SIMD intrinsic has the prototype:

uint8xl6x2_t vld2q_u8 (uint8_t const * ptr);

How many bytes does this intrinsic load from memory?

Which of the following is an accurate description of network storage as compared to on-chip RAM?

Which of the following is an optional extension to the ARMv7-A architecture?

Which of the following processor resources do NOT have to be saved or modified by the Linux scheduler during context switch?

It is common to declare structures as "packed" in order to minimize data memory size. Which of the following accurately describes the effect of this?

An advantage of native compiling over cross compiling is that:

An interrupt handler contains the following instruction sequence at the end. The purpose of these instructions is to clear the interrupt request in the interrupt controller and then safely re-enable interrupts.

STR r0, [r1] ; write to interrupt controller register to clear interrupt request

CPSIE i ; re-enable IRQ interrupts

Which of the following instructions should be placed at position

The following C function is compiled with hard floating point linkage.

float function(int a, float b, int c, float d);

Which register is used to pass argument c?

According to the AAPCS (with soft floating point linkage), when the caller "func" calls sprintf, where is the value of the parameter "x" placed?

#include

void func(double x, int i , char *buffer)

{

sprintf(buffer, "pass %d: value = %f\n", i, x); }

Consider a sequence of five independent instructions running on a pipelined processor. There are no interlocks and no data dependencies between instructions, and each instruction takes one cycle to execute. The processor has three pipeline stages and is not superscalar.

How many cycles does it take to fetch, decode and execute all five instructions in sequence, assuming that there are no pipeline stalls?

Which of the following is an advantage of the single-step debug technique?

Which of the following operations would count as intrusive to normal processor operation?

The effect of clicking the Stop button in a debugger is to:

A standard performance benchmark is being run on a single core ARM v7-A processor. The performance results reported are significantly lower than expected. Which of the following options is a possible explanation?

The disassembly of a program written in C shows calls to the function__aeabi_fadd. Which one of these compiler floating point options could have been used?

When setting the initial location of the stack pointer and the base address of the heap, the ARM EABI requires that the: